# A study of defects on EUV masks using blank inspection, patterned mask inspection, and wafer inspection

Sungmin Huh<sup>1</sup>, Liping Ren<sup>1</sup>, David Chan<sup>1</sup>, Stefan Wurm<sup>1</sup>, Kenneth Goldberg<sup>2</sup>, Iacopo Mochi<sup>2</sup>, Toshio Nakajima<sup>3</sup>, Masahiro Kishimoto<sup>3</sup>, Byungsup Ahn<sup>4</sup>, Inyong Kang<sup>4</sup>, Joo-on Park<sup>4</sup>, Kyoungyong Cho<sup>4</sup>, Sang-in Han<sup>5</sup>, Thomas Laursen<sup>5</sup>

SEMATECH 255 Fuller Road, Suite 309, Albany, NY 12203 USA

2-400, Lawrence Berkeley National Laboratory, Berkeley, CA 94720

3AGC Electronics America, 257 Fuller Road, Albany NY 12203

Samsung Electronics Co., San#16 Banwol-Dong, Hwasung-City, Gyeonggi-Do, Korea, 445-701

ASML, 25 Corporate Circle, Albany, NY 12203

#### **ABSTRACT**

The availability of defect-free masks remains one of the key challenges for inserting extreme ultraviolet lithography (EUVL) into high volume manufacturing, yet little data is available for understanding native defects on real masks. In this paper, a full-field EUV mask is fabricated to investigate the printability of various defects on the mask. The printability of defects and identification of their source from mask fabrication to handling were studied using wafer inspection. The printable blank defect density excluding particles and patterns is  $0.63/\text{cm}^2$ . Mask inspection is shown to have better sensitivity than wafer inspection. The sensitivity of wafer inspection must be improved using through-focus analysis and a different wafer stack.

Keywords: EUV, mask, phase defect, inspection

#### 1. INTRODUCTION

Over the past year, leading-edge chip manufacturers have shifted their interest towards the insertion of extreme ultraviolet lithography (EUVL). This emphasis is increasing the pressure to resolve defect-free blanks, which remains one of the key challenges impeding EUVL insertion into high volume manufacturing (HVM). The success of the industry's mask blank defect reduction effort critically depends on the timely availability of inspection tools that can precisely and reliably find ever smaller defects. However, to meet high volume manufacturing requirements for sub-32 nm half-pitch (HP) patterning, the industry needs a blank inspection tool and EUV aerial image measurement system (AIMS) to determine printability in the EUV wavelength (13.5 nm). However, an inspection tool to qualify EUV masks will not be available in the timeline for pilot line production or early HVM [1-2]. One full-field EUV patterned mask was fabricated in collaboration with a blank company and mask shop. Printable defects on the wafer were characterized using a deep ultraviolet (DUV) patterned mask inspection and wafer inspection tool. Exposures were done using the EUV alpha demo tool (ADT) at the College of Nanoscale Science and Engineering (CNSE) in Albany. After exposure, the wafers were inspected with a wafer inspection tool (KLA 28XX) at CNSE. Repeater analyses of wafer inspection and patterned mask inspection were used to classify all defects found during the wafer inspection. Using information from repeater defects, the definition of defects induced from the mask blank is discussed and ways to improve the sensitivity of wafer inspection tools for better qualification of the final EUV mask are proposed.

## 2. DEFECT ON EUV BLANK AND INSPECTION TOOL

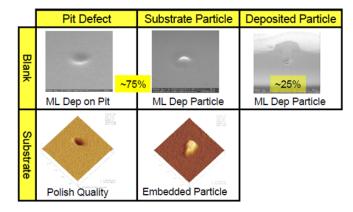

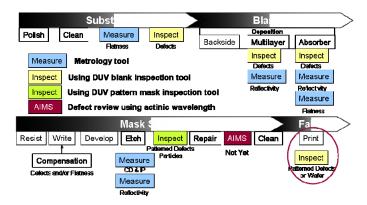

Three types of defects can be found on the blank level of an EUV mask: surface pits, which originate from the substrate pits that decorate during multilayer deposition; bumps or covered particles, which originate from embedded substrate particles or mechanical walk particles; and covered or partially covered defects added by the multilayer deposition process. Figure 1 shows defect types on the substrate and blank. Pit defects are the most dominant, accounting for on average 75% of the defects observed. Embedded particles on the substrate can be cleaned by an advanced cleaning process. The remaining 25% of the defects are due to particles deposited during the deposition process [3]. Figure 2 shows the EUV mask fabrication flow and the required metrology and inspection tools. A blank inspection tool, patterned mask inspection tool, and defect inspection using an actinic wavelength (EUV AIMS) are needed to qualify the mask. However, a blank inspection tool with sufficient sensitivity and an EUV AIMS are not currently available. Furthermore, it appears that this tool will not be available even for pilot line or early HVM operations. Consequently, the final EUV mask must be qualified by wafer inspection. It is therefore important to compare the sensitivity of each inspection tool to determine whether a wafer inspection tool can fully characterize potentially printable defects on EUV masks.

Figure 1. Types of defects on an EUV blank

Figure 2. EUV mask fabrication flow for pilot line application or early HVM

# 3. EXPERIMENTAL

## 3.1 Layout of the test mask and experimental procedure

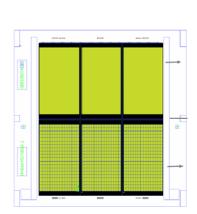

An EUV blank was fabricated in collaboration with commercial blank company and mask shop. We used a standard EUV mask fabrication process. The pattern layout of the mask is shown in Figure 3. There were 3 X 2 subfields for the repeater analysis for wafer inspection. The pattern size on the mask was 50nm 1:1 lines and spaces in wafer scale. A large critical dimension (CD) was selected to exclude resist effects such as linewidth roughness (LWR) during wafer

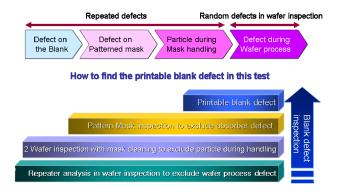

inspection. The experimental plan is explained in the Figure 4. After mask fabrication, patterned mask inspection was done to qualify defects on the patterned absorber. After that the mask was shipped from Asia to the USA without using a dual pod. Particles may be added to the mask during mask handling and shipping. These particles cannot be detected by a patterned mask inspection tool, However they will be detected as repeater defects on the wafer inspection tool. At CNSE in Albany, NY, the mask was exposed with the EUV ADT. Then the wafer was inspected with CNSE's KLA 28XX wafer inspection tool to classify printable pattern defects, blank defects, and particles. The mask was then sent back to Asia for cleaning to remove particles from the first ADT exposure. The cleaning removed all the particles, but other particles were added in different locations. One more ADT exposure and wafer inspection was done to exclude the particles on the EUV mask. When the coordinates of the wafer inspection overlap in first and second wafer inspection, they can be considered printable blank or pattern defects. However, when a coordinate does not overlap, it can be classified as a particle, as all particles are removed or added at different locations after mask cleaning. Figure 4 summarizes how to classify defects on the blank and patterned absorber, particles, and process defects. Figure 4 explains the classification procedure, which is outlined in more detail as follows:

- After repeater analysis, any random process defect can be excluded from the results of wafer inspection.

Repeated defects include blank defects, pattern defects, and particles.

- Two wafer inspections were conducted. After the first wafer inspection, the mask was shipped back to the mask shop and cleaned to remove the particle from the original site. Overlapping coordinates indicate blank defects and pattern defects. The others are particles added during mask shipping and handling.

- Patterned defects are excluded from the results of the repeater analysis using the information from patterned mask inspection. Finally, a printable blank defect can be obtained without the information from the blank inspection.

Figure 3. Mask layout

Figure 4. Experimental procedure

Figure 4. Procedure to identify defects from wafer inspection

#### 3.2 EUV ADT exposure & wafer inspection conditions

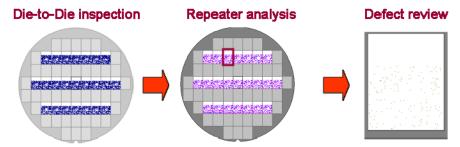

The wafers were printed using CNSE's EUV ADT with a NA of 0.25 and sigma of 0.5. SERV40, 80nm thick, was used for this test. The 26 die are arranged on the wafer at best dose and focus, which is shown in Figure 6. CNSE's KLA 28XX was used for die-to-die wafer inspection using a developed resist pattern. After repeater analysis, one die was chosen for review to classify the defects.

Figure 6. The procedure for wafer inspection and repeater analysis

#### 4. RESULTS AND DISCUSSION

#### 4.1 Patterned mask inspection

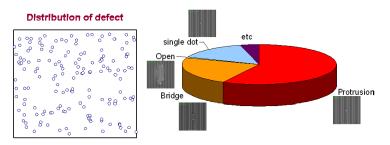

After patterning the absorber, the mask was inspected using a DUV patterned mask inspection tool with a wavelength of 257nm. The tool can inspect part of the inherent blank defects on the substrate and patterned defects generated during patterning of the absorber. Defects were classified as protrusion, bridge, open, single dot, etc. Figure 7 shows the distribution and Pareto chart classifying each defect. Protrusion and bridge types have the highest percentage. The printable/inspectable defects, printable/uninspectable defects, and unprintable defects are classified based on the inspection and defect review.

Figure 7. The result of patterned mask inspection

## 4.2 Repeater analysis during wafer inspection.

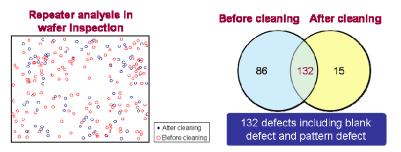

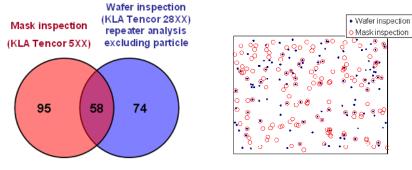

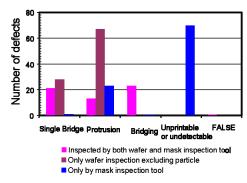

After repeater analysis, non-repetitive process defects can be excluded from wafer inspection. Two wafer inspections, including mask cleaning, were performed to classify particles added during mask handling and shipping. As a dual pod was not used when the mask was shipped from Asia to the USA, many particles can be added or removed by cleaning. However, when a dual pod is used for this kind of test, fewer particles are added. When the coordinates of the two inspection results are compared, a coordinate that is not overlapped is considered a particle, because all particles can be cleaned or moved to another location. Overlapped coordinates are classified as a printable pattern defect or blank defect. The first and second wafer inspections detected 218 and 147 repeated defects, respectively. Unoverlapped 86 and 15 defects from two repetitive wafer inspections were classified as particles, and 132 defects can be considered blank and patterned defects. This assumption is based on the fact that all particles could be cleaned during mask cleaning. The coordinates of the defects from wafer inspection and patterned mask inspection were compared to determine which patterned defect is detectable by patterned mask inspection. The rest of the defects can be considered printable blank defects, which are detected by wafer inspection tool (see Figure 9). Ninety-five defects were detected by patterned mask inspection, but not by wafer inspection. Fifty-eight defects were detected by both inspection tools. Seventy-four defects were detected by only the wafer inspection tool. Those can be considered printable blank defects. The printable blank defect density was  $0.63/\text{cm}^2$ .

Figure 8. Particles in the repeater analysis to extract defects on the blank and pattern

Ninety-five defects, which were detected by only the patterned mask inspection tool, were reviewed by wafer review scanning electron microscopy (SEM) to determine whether they are unprintable on the wafer or undetectable by the wafer inspection tool. Twenty-five defects were printable on the wafer, but not detected by the wafer inspection tool. The other 70 defects were unprintable on the wafer, which is why they could not be detected by the wafer inspection tool. Figure 10 shows the kinds of defects that are more detectable by the wafer inspection tool. Small defects such as protrusions are difficult to detect with the wafer inspection tool, but they can be detected with the patterned mask inspection tool. Large defects or bridge defects are easily detected by both inspection tools. From these results, the patterned mask inspection tool is more sensitive than the wafer inspection tool. We therefore need to find ways to improve the sensitivity of wafer inspection. SEMATECH is focusing on improving sensitivity using the two methods described below. Figure 11 shows some SEM images of the defects from this study.

(a) Comparison of mask inspection and wafer inspection (

(b) Coordinates of defects

Figure 9. Comparison of patterned mask inspection and wafer inspection

Figure 10. Comparison of sensitivity to defects on an EUV mask

|  |                |                                | On the mask | On the wafer |

|--|----------------|--------------------------------|-------------|--------------|

|  | Blank defect   |                                | No image    |              |

|  | Pattern defect | Detected by wafer inspection   | >           |              |

|  |                | Undetected by wafer inspection | ÷           | No Image     |

|  | Particle       |                                | No image    |              |

Figure 11. SEM images of defects at various locations

# 4.3 Strategy of sensitivity improvement on wafer inspection.

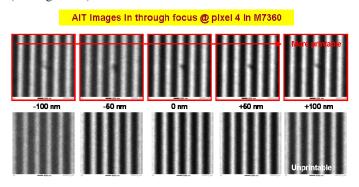

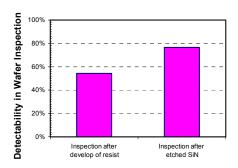

Phase defects on mask blanks have a strong focus-dependent printability on the wafer. The printability of pits and bumps is opposite from through focus. Figure 11 shows some AIT review images of blank defects on the mask [4]. Each defect has a different printability at through focus [5]. This means that through-focus wafer inspection can improve the detectability of the wafer inspection tool. Wafer inspection of the exposed sample from through focus can improve the sensitivity toward blank defects. Defect printability depends on size, profile, and location. Furthermore, different wafer stack will induce different sensitivity. Wafer inspection is less sensitive toward developed resist images than SiN wafer stacks because of the improved contrast in the pattern of the SiN stack on the wafer in the wavelength of the inspection source. An improved wafer inspection sensitivity of about 20% has been demonstrated using an underlayer stack (SiN) rather than developed resist (see Figure 12).

Figure 11. AIT images in through focus @ pixel 4 in M7360

Figure 12. Improved wafer inspection sensitivity using a different wafer stack.

#### 5. CONCLUSION AND FUTURE WORK

The identification of defects on EUV mask blanks is a key technology for EUV lithography when used in mass production. SEMATECH, in collaboration with industry, is evaluating defect printability on EUV masks using ADT, AIT, and wafer inspection tools. In this paper, the printability of defects and identification of their source from mask fabrication to handling were studied using wafer inspection. Blank defects, patterned defects, and particles were classified using repeater analysis on the wafer inspection. Blank defects should be quantified in the mask shop or blank company; particle defects should be quantified and controlled in the wafer fab. However, printable blank defect density excluding particle adders and patterned defects is indirectly quantified during wafer inspection, resulting in 0.63/cm² for this particular EUV mask. Mask inspection is more sensitive than wafer inspection. Small defects on the mask may be unprintable or undetectable by wafer inspection only. Therefore, the sensitivity of wafer inspection must be improved using through-focus analysis and a different wafer stack. SEMATECH continues to focus on improving the sensitivity of wafer inspection. So far, improved sensitivity of about 20% has been demonstrated using an underlayer stack (SiN).

### REFERENCES

- 1. Huh, S., Kearney, P., Wurm, S., Goodwin, F., Han, H., Goldberg, K., Mochi, I., Gullikson, E., "EUV actinic defect inspection and defect printability at the sub-32-nm half-pitch," Proceedings of SPIE Vol. 7470, 74700Y (2009).

- 2. Stefan Wurm, Hakseung Han, Patrick Kearney, Wonil Cho, Chan-Uk Jeon, and Eric Gullikson, Proc. SPIE 6607, 66073A, (2007).

- 3. Yun, H., Goodwin, F., Huh, S., Orvek, K., Cha, B., Rastegar, A., Kearney, P., "SEMATECH EUVL mask program status," Proceedings of SPIE Vol. 7379, 73790G (2009).

- 4. K. A. Goldberg, S. B. Rekawa, C. D. Kemp, A. Barty, E. H. Anderson, P. Kearney, H. S. Han, Proc. SPIE 6921, 69213U (2008).

- 5. Huh, S., Kearney, P., Wurm, S., Rastegar, A., Goodwin, F., Goldberg, K., Mochi, I., Nakajima, T., Kishimoto, M., Komakine, M. "A Study of Real Native Defects on EUV Mask Blanks Using a DUV Blank Inspection Tool and SEMATECH AIT," EUVL Symposium, 2009